# <u>Convertisseurs</u> Analogique - NUMÉRIQUE

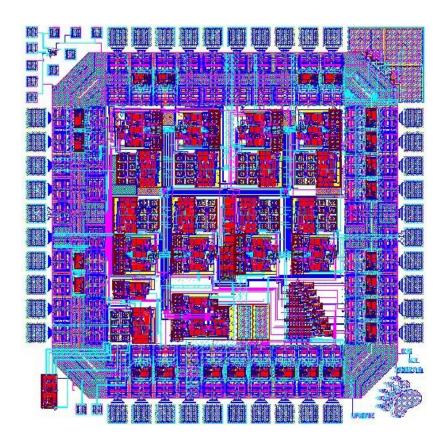

Convertisseur pipelined 5MHz 10 bits Dimension :  $1.5 \cdot 1.5 \text{ mm}$  30 résistances, 305 condensateurs, 2073 PMOS, 2854 NMOS Année 2002

CPNV

<u>Jean-François Pochon</u>

<u>www.electrons.ch</u>

Février 2005

## Table des matières

| TABLE DES MATIERES                              | 2  |

|-------------------------------------------------|----|

| THEORIE DE LA CONVERSION A/D                    | 3  |

| QUANTIFICATION:                                 | 3  |

| CRITERE DE NYQUIST (DE SHANNON):                |    |

| REPLIEMENT SPECTRAL:                            |    |

| FILTRE ANTI-REPLIEMENT:                         |    |

| RESTITUTION ET LISSAGE:                         |    |

| RAPPORT SIGNAL SUR BRUIT SNR (SNRWH):           |    |

| RAPPORT SIGNAL SUR BRUIT ET DISTORSION SINAD :  |    |

| NOMBRE EFFECTIF DE BITS ENOB:                   |    |

| TOPOLOGIES DE CONVERTISSEURS                    | 8  |

| Convertisseur Flash parallele.                  | 8  |

| CONVERTISSEUR A APPROXIMATION SUCCESSIVE        | 10 |

| CONVERTISSEURS A/D PIPELINED (SUBRANGING)       | 11 |

| Convertisseur sigma delta ( $\Sigma\Delta$ )    |    |

| CONFIGURATION D'UN AD/DA A CAPACITES COMMUTEES: | 14 |

| ERREUR D'OUVERTURE (JITTER)                     | 17 |

| ERREUR DE GITE DE FREQUENCE D'ECHANTILLONNAGE:  | 18 |

| REFERENCE DE TENSION:                           |    |

| PRECISION DU SIGNAL D'ENTREE :                  | 19 |

| MESURES ET TEST DE CONVERTISSEURS               | 20 |

| TEST STATIQUE:                                  | 20 |

| METHODE « DOS A DOS » :                         |    |

| TEST PAR HISTOGRAMME:                           | 21 |

| LIENS :                                         | 22 |

| EXERCICES                                       |    |

| EVEMDI EC DE DATA CHEET                         | 24 |

#### Théorie de la conversion A/D

Un petit chapitre théorique permet de se familiariser avec les diverses dénominations et de placer quelques notions clé pour l'étude de la numérisation.

#### Quantification:

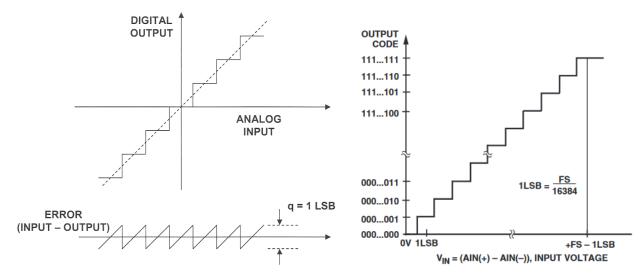

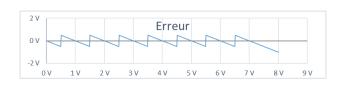

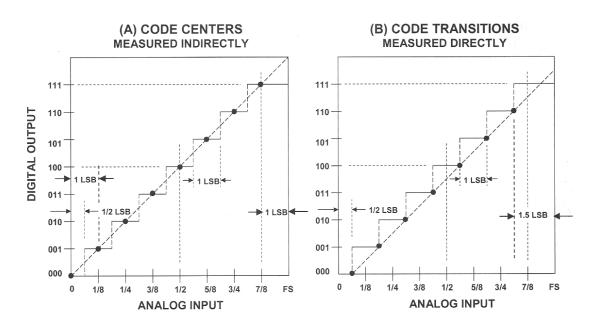

Figure 1: Erreur (bruit) de quantification

Si l'on considère un convertisseur parfait, la numérisation, ou quantification, va introduire une erreur car on ne passe pas sans conséquence d'une infinité analogique de points à quelques valeurs numériques prises sur le signal. Cette erreur en dents de scie (pour un signal de type triangle) peut se calculer par la racine de l'intégration du carré du signal, selon la définition de la valeur efficace.

$$e(t) = \sqrt{\frac{s}{q} \cdot \int_{-q/2s}^{q/2s} (st)^2 dt} = \frac{q}{\sqrt{12}}$$

$avec \quad q: valeur \left[V\right] d'un \ LSB$

s : pente [V/s] de la courbe.

Cette valeur est calculée sur la base d'un signal triangulaire mais c'est aussi une valeur reconnue pour les autres types de signaux.

La valeur rms d'un signal pleine échelle est quant à elle de

$$U_{rms} = \frac{q \cdot 2^N}{2 \cdot \sqrt{2}}$$

Le rapport signal sur bruit dû à cette erreur peut dès lors être calculé :

$$SNR = 20\log\left(\frac{q \cdot 2^{N} / (2 \cdot \sqrt{2})}{q / \sqrt{12}}\right) \text{ ce qui donne} \qquad \boxed{SNR = 6.02 \cdot N + 1.76 \text{ dB}}$$

JPN 3/26 Avril 2023

#### Critère de Nyquist (de Shannon):

Lors de la prise d'échantillons, il est une question que l'on ne peut pas éluder et qui est celle de la fréquence d'échantillonnage.

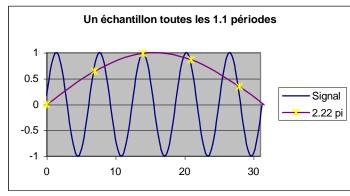

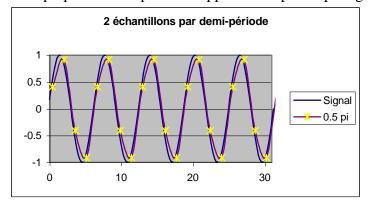

On peut voir sur ce graphique que si l'on échantillonne le signal à un rythme qui correspond à moins de deux échantillons par période (tous les  $\pi$ ) on n'obtient pas, lors de la restitution, un signal de fréquence équivalente.

Le signal numérisé est ici tracé après lissage.

Les valeurs numériques sont représentées par les petites croix.

Echantillonnage en prélevant un échantillon par demi-période : on assure la capture de la fréquence du signal considéré, mais pas forcément avec la bonne amplitude.

Quatre échantillons par périodes : nous assurons un échantillonnage de la fréquence correcte et une acquisition de l'amplitude qui peut suffire pour des applications pas trop exigeantes.

En pratique et si l'on tient à une image fidèle de notre signal échantillonné, une fréquence d'échantillonnage de 7-10 fois la fréquence du signal le plus rapide sont des valeurs correctes.

JPN 4/26 Avril 2023

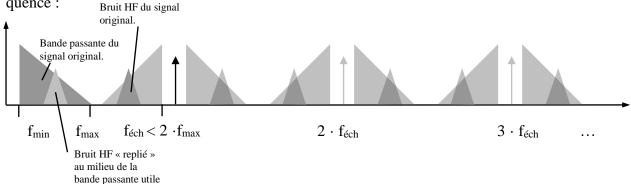

#### Repliement spectral:

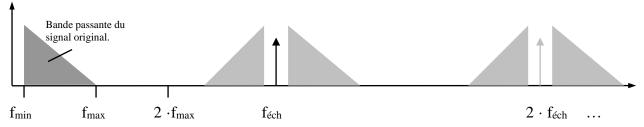

Si l'on passe du domaine temps au domaine des fréquences, on peut observer le phénomène suivant lors de l'observation du spectre d'un signal échantillonné :

Dans cet exemple on peut constater que l'on a utilisé une fréquence d'échantillonnage largement supérieure au double de la fréquence maximum du signal et d'autre part que le spectre représentant les valeurs échantillonnées est très étendu car il se répète tous les multiples de  $f_{\text{échantillonnage}}$ . On peut également remarquer la réplication inversée du spectre à gauche de la fréquence d'échantillonnage et de ses multiples.

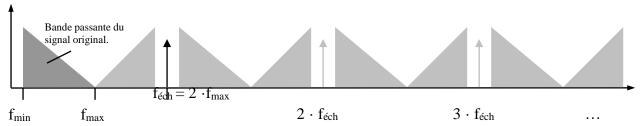

Diminuons maintenant la fréquence d'échantillonnage à la valeur minimum correspondante au critère de Nyquist :

On voit ici que le signal échantillonné de la deuxième zone (inversé) touche la bande passante originale du signal. Ce cas est un cas limite et on voit ici poindre un effet qui se nomme « repliement spectral » (aliasing dans le texte) ou l'on voit la réplique inversée du spectre se superposer au spectre initial.

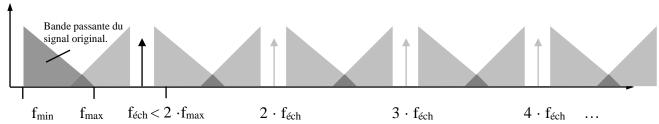

#### Signal sous échantillonné:

Ce type de spectre est l'image d'un signal que l'on a sous échantillonné, et on voit les zones sombres qui sont les zones de recouvrement spectral. A éviter absolument.

Il semble évident dès lors que l'on doit respecter la règle du double de la fréquence maximum du signal et on serait tenté de rire doucement des développeurs pris en flagrant délit de repliement. Nous allons voir que malgré ces bonnes résolutions, nous ne sommes pas encore à l'abri de ce piège.

JPN 5/26 Avril 2023

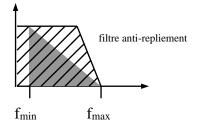

#### Filtre anti-repliement:

Observons ce qui se passe lors de l'échantillonnage d'un signal comportant du bruit haute fréquence :

Bruit HE du signal

Le bruit haute fréquence initial se retrouve au milieu de la bande passante et va se superposer au signal utile. Pour se prémunir de ce genre de problème, une solution simple consiste à utiliser un filtre anti-repliement .

Ce filtre va éliminer en amont (avant l'échantillonnage) les fréquences supérieures à la fréquence maximum utile du signal à échantillonner et ainsi empêcher, p. ex du bruit, de se retrouver au milieu de la bande utile après échantillonnage.

Ce type de filtre se place entre l'amplification et l'échantillonneur, afin de se prémunir du bruit éventuel amené par l'amplification.

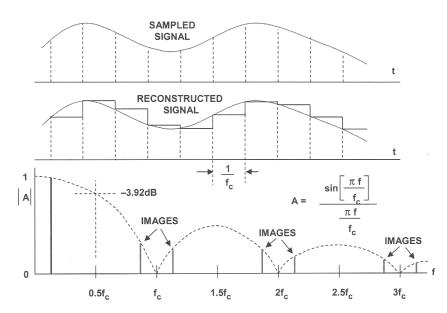

#### Restitution et lissage:

Les spectres illustrés cidessus sont des spectres de valeurs échantillonnées, il est évident que lors de la reconstruction du signal, on va « boucher les trous » entre les valeurs ne serait-ce qu'en maintenant la dernière valeur en attendant de recevoir la nouvelle. Le spectre s'en trouve modifié et un filtrage adapté va achever de nous débarrasser des résidus HF réplication dus l'échantillonnage.

Figure 2: Reconstruction du signal

JPN 6/26 Avril 2023

#### Rapport signal sur bruit SNR (SNRWH):

Signal to Noise Ratio est le rapport entre la valeur RMS de l'amplitude du signal sinus de test et la valeur RMS de la somme des amplitudes de toutes les autres fréquences excepté la tension continue et les 5 premières harmoniques du signal.

SNRWH est équivalant à SNR et le doux diminutif de Signal to Noise Ratio Without Harmonics.

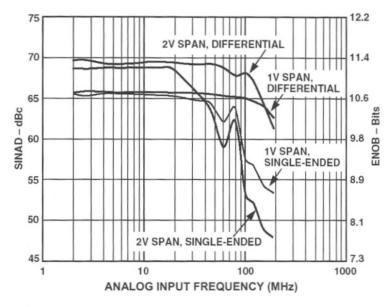

#### Rapport signal sur bruit et distorsion SINAD:

Rapport entre la valeur RMS du signal sinus de test et la valeur RMS de la somme des amplitudes de toutes le autres fréquences présentes dans le signal sauf la tension continue.

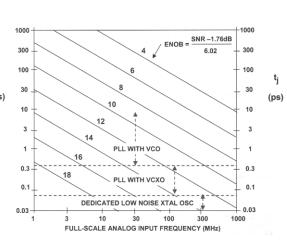

#### Nombre effectif de bits ENOB:

ENOB *Effective Number Of Bits* est une mise en évidence efficace des limitations d'un convertisseur A/D. Ce paramètre illustre la précision effective de votre convertisseur une fois les différentes erreurs additionnées. On s'aperçoit ainsi que le magnifique convertisseur 16 bits acheté très cher a en fait une largeur de code utile en sortie de, par exemple, seulement 8 bits...

Le calcul de ENOB est basé sur la valeur du SINAD et est donnée en retournant la formule :

$SNR = 6.02 \cdot N + 1.76 \, dB$ , ce qui donne :  $N = (SNR - 1.76 dB) / 6.02 \equiv ENOB$

### SINAD, ENOB, and SNR

Figure 3: Exemple de courbe pour un convertisseur 12 bits (AD 9226)

JPN 7/26 Avril 2023

#### Topologies de convertisseurs.

#### Convertisseur Flash parallèle.

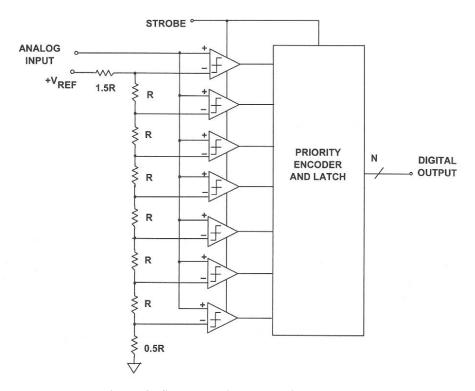

Ce convertisseur est le plus rapide des convertisseurs. Un convertisseur de N bits est constitué de 2<sup>N</sup> résistances et de 2<sup>N</sup>-1 comparateurs.

Chaque convertisseur a un seuil fixe définit par le réseau de résistances qui est 1 LSB plus élevé que le seuil du comparateur précédent.

Les comparateurs fournissent une valeur « thermométrique » de la conversion Analogique-Numérique qui doit être décodée pour être lisible en valeur binaire.

Figure 4 : Structure d'un convertisseur Flash

Il apparaît sur le schéma que la valeur analogique d'entrée est convertie en valeur numérique de manière asynchrone par les comparateurs et que c'est l'horloge du décodeur qui va dicter le nombre d'échantillons lus par seconde.

La vitesse actuelle des plus rapides son de l'ordre du GHz avec une précision de 8 bits.

Les limitations de ce type de convertisseur sont dues à la complexité de fabrication pour des convertisseurs plus précis. En effet, la précision maximum est de 10 bits en pratique, ce qui représente déjà  $2^{10}$ -1 = 1023 comparateurs.

Multipliez le nombre de comparateurs par la consommation de comparateurs haute vitesse et vous obtenez un IC qui consomme plusieurs Watt.

Ajoutez à cela la complexité que requière l'implémentation d'un nombre si élevé de comparateurs et vous aurez compris que le prix d'un convertisseur rapide et précis ne sera pas à la portée du premier budget venu.

JPN 8/26 Avril 2023

#### Et pourquoi il y a « 0.5R » en haut et en bas du pont diviseur ?

Pour comprendre on peut utiliser un exemple simple :

- Un convertisseur 3 bits

- Sur 8V (1 LSB = 1V)

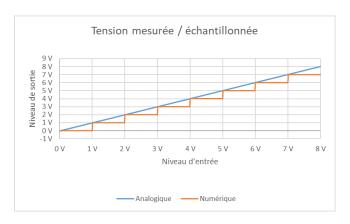

Si on met 8 résistances égales, elles définissent les seuils suivants : 1,2,3,4,5,6,7 V pour les 7 comparateurs. Le résultat est que **jusqu'au seuil de la première résistance, on a toujours zéro en sortie**, en graphique, ça donne ça : entrée analogique en bleu, sortie numérique « re-convertie » en orange.

Défaut à cette méthode : La tension équivalente numérique est « toujours trop basse », puisque l'erreur est toujours dans le même sens et a une valeur max de 1 LSB.

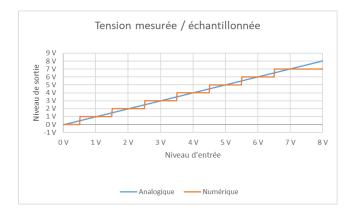

C'est gênant d'introduire une erreur persistante dans notre signal, on cherche une meilleure idée : placer les seuils « décalés de ½ LSB » et à 0.5V, il passe déjà au code de sortie suivant.

Remarque : on doit mettre une résistance de ½R pour avoir un seuil de commutation à 0.5V, puis à 1.5V, etc. Du coup, l'erreur est plus équilibrée et de seulement + ou – la tension de ½ LSB

**Défaut :** on voit que de 6.5 à 8V, il y a 1.5V où on change la tension d'entrée sans que la tension de sortie ne varie, ce qui génère une plus grande erreur et pourrait être problématique... mais pas tant que cela, car dans un système de numérisation, on évite absolument de se trouver en saturation (déformation grave des signaux) cela implique qu'on laisse « un peu de distance » entre la tension de référence du convertisseur (tension max utilisable) et la valeur max réelle des signaux d'entrée.

JPN 9/26 Avril 2023

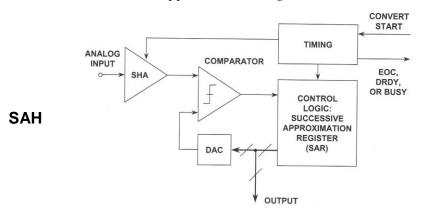

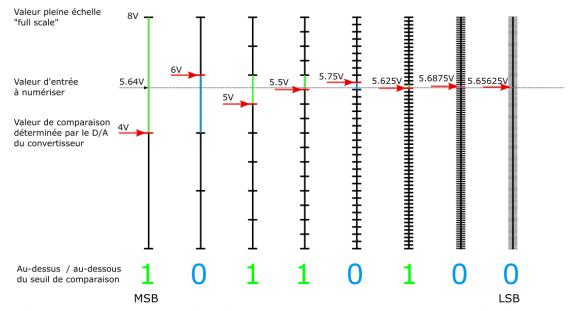

#### Convertisseur à approximation successive

Ce convertisseur est le plus répandu actuellement pour les besoins standards de conversion A/D. Les vitesses de conversion se situent dans les MHz pour un convertisseur 8 bits et on trouve des convertisseurs qui ont une résolution jusqu'à 18 bits à des prix normaux. La dénomination usuelle de la littérature est SAR *Successive Approximation Register*.

Figure 5: Structure d'un convertisseur SAR

Ce convertisseur va « essayer » plusieurs valeurs en comparant la valeur déterminée par la logique de commande avec la valeur d'entrée.

Objectivement, on sait que la valeur est entre 5.625 et 5.65625V rien de plus.

Le temps de conversion serait directement proportionnel au nombre de bits si le temps de conversion pour une précision de p.ex 16 bits était le même que pour une précision moindre, ce qui n'est hélas pas le cas, on doit laisser plus de temps de stabilisation aux signaux pour une meilleure précision.

A noter que la précision du convertisseur SAR est largement dépendante de la précision du convertisseur D/A interne. Les bons convertisseurs étaient réalisés avec des résistances ajustées au laser, ce qui impliquait un fort coût de fabrication. Les nouvelles conceptions s'appuient sur des architectures à capacités commutées qui se passent de résistances de précision.

JPN 10/26 Avril 2023

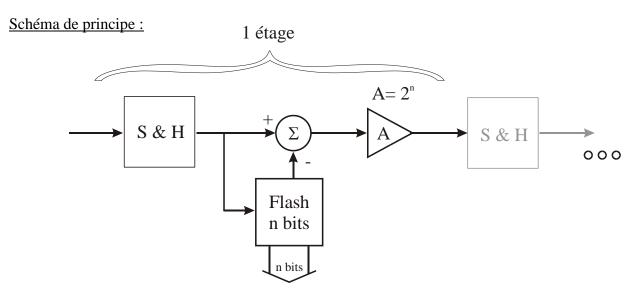

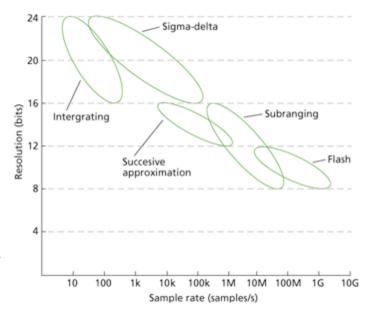

#### Convertisseurs A/D Pipelined (Subranging)

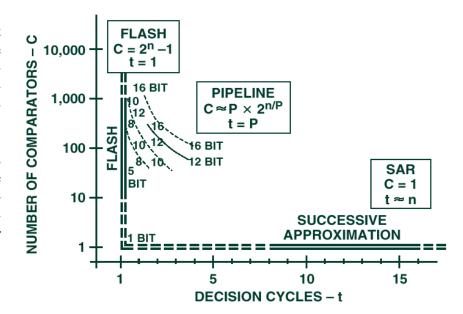

Si l'on regarde les différents types de comparateurs Analogique-Numérique, on s'aperçoit que ou il est rapide (conversion en 1 coup de clock pour le Flash) mais il est cher et se limite à 10 bits (pour un coût raisonnable). Ou il est précis mais plus lent, un coup de clock par bit pour l'approximation successive (SAR) ou un temps variable et plutôt long pour le double rampe.

Il existe sur le marché un nouveau type de convertisseur qui permet d'être rapide, précis et tout cela sans la débauche de comparateurs des convertisseurs Flash.

Figure 6: Un étage de convertisseur pipelined

#### Déroulement d'une conversion :

Dans l'exemple : Premier étage d'un convertisseur 12 bits à 4 étages.

JPN 11/26 Avril 2023

#### Convertisseur sigma delta ( $\Sigma\Delta$ )

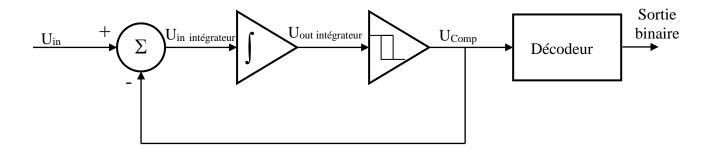

Le convertisseur double rampe que l'on présente souvent avec une rampe de charge à temps constant (le courant dépend de la tension d'entrée) et une rampe de décharge à courant constant (le temps dépend du nombre de charges accumulées dans le condensateur) a évolué vers le  $\Sigma\Delta$  que l'on reconnaît dans le schéma suivant :

Nous avons donc un soustracteur, un intégrateur, un comparateur en trigger de schmit et un décodeur.

Il faut ajouter que la sortie  $U_{comp}$  du comparateur (qui sera soustraite au signal d'entrée) a une amplitude de variation qui est de l'ordre de la plage de mesure (p.ex. 10V).

Partons maintenant à zéro pour une conversion :

Tension d'entrée : faible

Avec une tension d'entrée faible (1V), la tension de sortie de l'intégrateur va augmenter lentement et il faudra un certain temps avant que le seuil de trigger supérieur soit atteint. Lors de la commutation du trigger, on se retrouve avec une tension négative très importante sur l'intégrateur(1-10 = -9V), ce qui va précipiter la descente de sa tension de sortie jusqu'au seuil bas et le cycle recommence.

La valeur de sortie du comparateur, si on la prélève à chaque coup de clock (déterminé par la circuiterie externe) va ressembler à la suite de 0 et de 1 qui figure au bas du graphique.

Si, maintenant, on déplace la tension d'entrée vers le haut de la plage de mesure (9V), la montée de la sortie de l'intégrateur va être beaucoup plus rapide et à l'invers la descente plus lente

Vous l'avez deviné, c'est la « densité » de 1 dans cette chaîne de nombres qui déterminera la valeur binaire de sortie.

JPN 12/26 Avril 2023

#### Avantages du $\Sigma\Delta$ :

Ce convertisseur est très utilisé lorsque l'on veut une conversion précise (24 bits !) il équipe donc la quasi totalité des multimètre de nos laboratoires.

Plusieurs facteurs plaident en sa faveur, notamment l'intégration en continu du signal d'entrée, ce qui permet de s'affranchir des variations périodiques du signal d'entrée (bruit) dont on prend la valeur moyenne durant la mesure.

A contrario, dans le cas du pipelined, l'échantilloneur-bloqueur peut très bien garder une valeur qui aura été prélevée sur une crête due au bruit, ce qui va fortement influencer le résultat de la conversion.

De plus la mesure peut être effectuée une multitude de fois (oversampling) avant d'afficher la valeur moyenne des résultats de conversion, ce que font les multimètres qui vous donnent le choix d'avoir un rafraîchissement très rapide, mais seulement 3 digits affichés, ou 6-8 digits, avec une fréquence de rafraîchissement plus lente.

On peut ajouter que, comme le double rampe, ce type de convertisseur est indépendant des variation lentes de la résistance ou du condensateur d'intégration (température, vieillissement) car on charge et on décharge à travers les mêmes éléments, une variation p. ex. de la résistance, influence la pente de montée comme la pente de descente.

#### Inconvénients:

Il va de soit que ce genre de convertisseur est lent et ne permet pas de rivaliser avec ses confrères SAR ou Flash sur le plan de la vitesse.

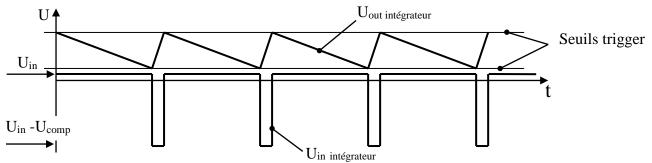

#### Effet sur le bruit de quantification :

Figure 7: Suréchantillonnage, Filtre digital, mise en forme du bruit et décimation.

On peut voir sur cette image l'effet du suréchantillonnage Oversampling et de la décimation sur le niveau de bruit de quantification compris dans la mesure.

La mise en forme du bruit *Noise Shaping* est acomplie par le filtre analogique de l'intégrateur qui a un comportement passe haut pour le bruit et un comportement passe bas pour le signal utile.

JPN 13/26 Avril 2023

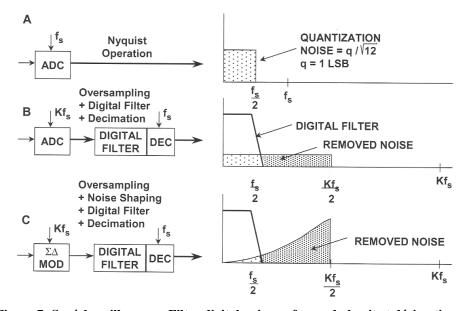

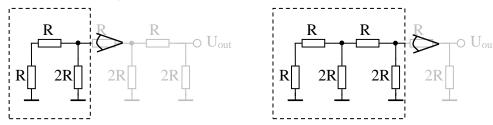

#### Configuration d'un D/A à réseau de résistances R-2R

On trouve un montage à ampli op sommateur qui permet de transformer un chiffre binaire en une tension en volt, en utilisant des valeurs pour chacune des résistances qui correspondent au poids de chacun des bits.

Le plus simple et le plus utilisé est un autre montage, le réseau de résistances R-2R, décrit cidessous.

Ce réseau de résistances a ceci de particulier que lorsque l'on isole à partir de la gauche une partie du schéma après n'importe quelle résistance de valeur 2R, on trouve une valeur de résistance équivalente égale à R. Et vu sous l'angle de la résistance équiva-

lente de Thévenin, cela ne fait aucune différence si on branche cette résistance à Vcc ou à 0V

Lorsque l'on met une des branches à Vcc (5V p.ex) on peut calculer la tension qui apparaît sur la sortie du montage : on voit dans le schéma équivalant de droite qu'il s'agit de 2.5 V divisé par deux, puis divisé encore par deux, ce qui fait 0.625V. On a donc affaire au LSB du montage.

Lorsque l'on positionne la résistance 2R suivante à Vcc, le schéma équivalent est le suivant : on a une source de 2.5V  $R_{th}$ =R que l'on va aussi diviser par deux, mais une seule fois  $\Rightarrow$  +1.25 V sur Uout.

Pour la dernière résistance 2R, on aura directement 2.5V sur la sortie, c'est le MSB.

Nous avons illustré ici un convertisseur 3 bits, mais il est extensible à volonté.

JPN 14/26 Avril 2023

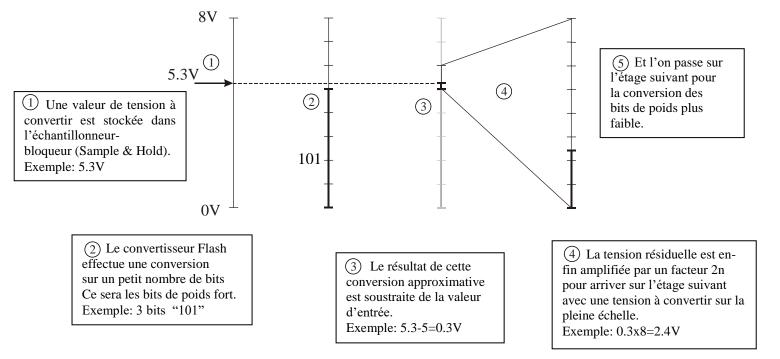

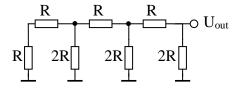

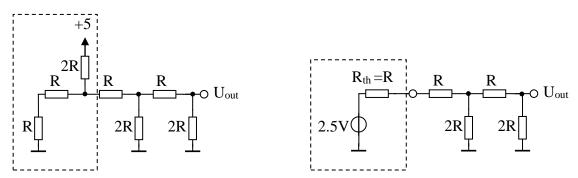

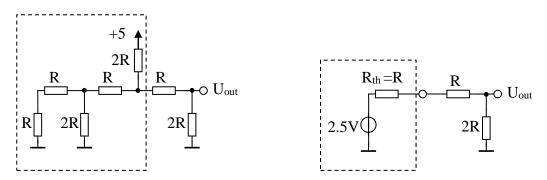

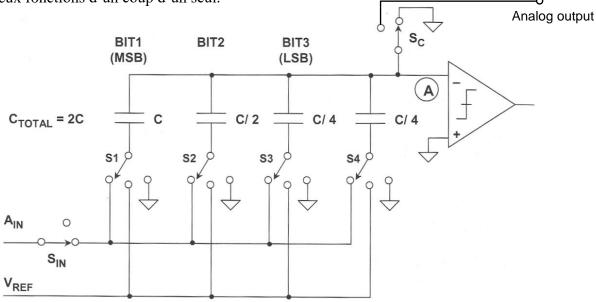

#### Configuration d'un AD/DA à capacités commutées :

On doit, dans l'architecture Pipelined, faire une conversion approximative (Flash) et soustraire le résultat de cette conversion à la valeur analogique de l'entrée de l'étage. Ce montage va réaliser ces deux fonctions d'un coup d'un seul.

Figure 8: Switches dans la position poursuite du signal "échantillonage"

Remarquez le condensateur additionnel connecté à S<sub>4</sub>, ce condensateur n'est là que pour terminer la chaîne et compléter la valeur des condensateurs à 2C. Le fonctionnement de ces condensateurs est similaire à un réseau R/2R à la différence que l'on a mis des condensateurs à la place des résistances.

Pour comprendre le fonctionnement de ce circuit, il faut l'étudier étape par étape :

- Les switches sont dans l'état représenté et les condensateurs se chargent tous à la même valeur V<sub>Ain</sub> déterminée par la tension d'entrée.

- On ouvre le commutateur  $S_{\rm IN}$  et le commutateur  $S_{\rm C}$ , ce qui déconnecte l'entrée de mesure et libère le point A de sa connexion à la masse. Ce point est maintenant flottant.

- On commute tous les switches sur la masse, une tension de -A<sub>IN</sub> apparaît au point (A)

- Si on positionne S<sub>1</sub> sur V<sub>ref</sub>, une tension de Rref/2 est ajoutée à -A<sub>IN</sub>. Le comparateur peut alors décider du bit de poids fort en fonction de la sortie digitale. Si on n'a pas atteint 0V, alors on garde S<sub>1</sub> dans cette position et on passe à S<sub>2</sub>. Sinon, on remet S<sub>1</sub> dans la position initiale et on passe à S<sub>2</sub>.

- On positionne S<sub>2</sub> sur Vref, ...

La conversion est terminée lorsque l'on a pris la décision après la commutation de  $S_3$ .  $S_4$  n'est jamais commuté sur  $V_{ref.}$ . Le temps pour réaliser ces opérations dépend des temps d'établissement analogique des tensions et on peut imaginer que ce fonctionnement soit plus rapide que le clock, ce qui permet une conversion « en temps caché » en moins d'un clock. Ce système permet de faire une conversion A/D partielle et de lire le résidu analogique (inférieur à 1 LSB) sur la sortie analogique, prête pour être amplifiée et « passée » à l'étage suivant.

Dans cette architecture à condensateurs, on peut placer des capacités en parallèle que l'on peut ajouter ou pas à C, C/2, C/4. Cela permet d'ajuster leur valeur au cours de cycles d'autocalibration (MAX1200) et compenser, par exemple, des dérives thermiques ou le vieillissement.

JPN 15/26 Avril 2023

#### Comparateurs:

Ce mode de conversion permet de limiter de manière drastique le nombre de comparateurs nécessaire à la conception d'un convertisseur flash de même précision.

Un convertisseur Flash 10 bits nécessite l'implémentation de 1023 comparateurs dans le composant. Le coût du chip s'en ressent et 10 bits est une valeur maximum pour cette technologie.

Par comparaison, un convertisseur Pipelined à trois étages de 4

bits a une précision de 12 bits et nécessite seulement l'utilisation de 3 x 15=45 comparateurs.

Si l'on veut calculer le nombre de comparateurs nécessaires à la conception d'un convertisseur quelconque, la formule est la suivante:

Nombre de comparateur =  $2^{(n/p)}$  - 1 x p

Avec:

n : nombre de bits du convertisseur.

p : nombre d'étage du convertisseur.

#### Vitesse:

La vitesse de conversion d'un convertisseur Pipelined est semblable à celle d'un Flash à un retard (plus un petit délais pour les temps d'établissement analogiques) près. En effet, pour le premier échantillon, il faudra attendre un nombre de coup de clock égal au nombre d'étages avant d'avoir la conversion disponible à la sortie.

A partir de ce moment, un échantillon sortira à chaque coup de clock comme pour le convertisseur Flash. Il n'en demeure pas moins que le convertisseur représente un retard dont il faut tenir compte, par exemple dans une boucle de réglage ou dans un fonctionnement ou l'on ne fait qu'une conversion.

Figure 9 http://www.reed-electronics.com How do ADCs work? 07 2002

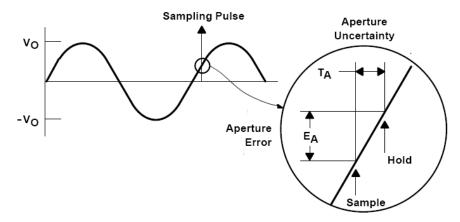

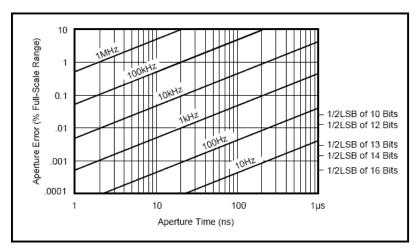

#### Erreur d'ouverture (jitter)

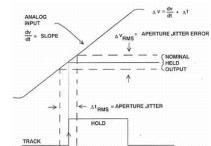

Lors de la prise d'échantillon de l'échantillonneur, une incertitude persiste quant à l'instant auquel on a bloqué effectivement la valeur. Car bien que les temps de réaction soient courts, et notamment pour des signaux rapides, cette incertitude peut avoir des impacts non négligeables.

Figure 10: Erreur d'ouverture de l'échantillonneur bloqueur

La fréquence maximum d'échantillonnage est en particulier affectée car le temps d'incertitude d'ouverture associée à la tension d'erreur parcourue par le signal durant ce temps là. Sachant que le maximum d'erreur possible qui ne génère pas d'erreur est ½ LSB, On peut calculer la fréquence maximum que permet cette erreur d'ouverture.

Pente max d'un signal sinusoïdal :

Tension d'erreur max permise en fonction de  $\hat{U}$  et de N

$$dv/dt = \hat{U} \cdot 2\pi \cdot f \ \ \lceil \ \ E_A \!\!=\!\! \hat{U} \! \cdot 2\pi \cdot f \cdot T_A$$

$$U_{(1/2 LSB)} = \frac{2 \cdot \hat{U}}{2^{N+1}}$$

On obtient la fréquence max. opérationnelle du convertisseur en égalisant ces deux équations :

$$f = \frac{1}{T_A \cdot \pi \cdot 2^{N+1}}$$

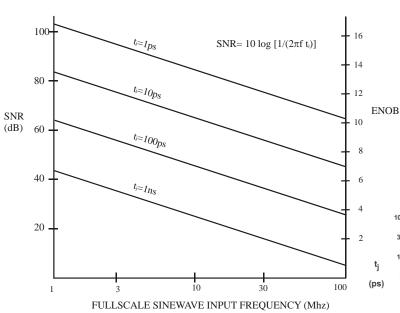

Figure 11: Erreur d'ouverture en fonction de f et de N

Où l'on constate qu'un bon échantillonneur bloqueur est primordial pour les convertisseurs haute vitesse.

JPN 17/26 Avril 2023

#### Erreur de gigue de fréquence d'échantillonnage :

Dans un monde parfait, l'horloge de pilotage du convertisseur n'est jamais perturbée et elle arrive telle la cavalerie, toujours à l'heure. Il n'en est rien en réalité et dans des applications rapides ou lorsque le clock est de type rustique, on peut voir apparaître une diminution du rapport signal sur bruit non négligeable, due à l'erreur de gigue (jitter).

On peut également « retourner » ce graphique et se poser la question de la précision du générateur de clock pour assurer un jitter déterminé.

JPN 18/26 Avril 2023

#### Référence de tension :

S'il est évident que la précision du convertisseur ne peut pas être supérieure à la référence de tension sur laquelle il s'appuie, on n'a pas toujours conscience des tolérances que cela implique.

Voici un tableau qui indique pour différentes résolutions usuelles, la précision de la référence de tension à mettre en œuvre afin d'assurer la conversion pour une variation de température de 100°C

|      |                            |                                  | SB WEIGHT ( |      |

|------|----------------------------|----------------------------------|-------------|------|

|      |                            | 10, 5, AND 2.5V FULLSCALE RANGES |             |      |

| BITS | REQUIRED<br>DRIFT (ppm/°C) | 10V                              | 5V          | 2.5V |

| 8    | 19.53                      | 19.53                            | 9.77        | 4.88 |

| 9    | 9.77                       | 9.77                             | 4.88        | 2.44 |

| 10   | 4.88                       | 4.88                             | 2.44        | 1.22 |

| 11   | 2.44                       | 2.44                             | 1.22        | 0.61 |

| 12   | 1.22                       | 1.22                             | 0.61        | 0.31 |

| 13   | 0.61                       | 0.61                             | 0.31        | 0.15 |

| 14   | 0.31                       | 0.31                             | 0.15        | 0.08 |

| 15   | 0.15                       | 0.15                             | 0.08        | 0.04 |

| 16   | 0.08                       | 0.08                             | 0.04        | 0.02 |

Figure 12: Tolérances admissibles pour la référence de tension  $\Delta\theta$ =100°C

Les prix des références de tension sont bien sur liés à leur précision et si on trouve des précisions de 3 ppm/°C pour 1 dollars, les références à 1.5 ppm/°C sont déjà 10 fois plus chères. Elles permettent par contre une prise en compte des variations de température via une entrée qui permet la correction de la tension de sortie en fonction de la température.

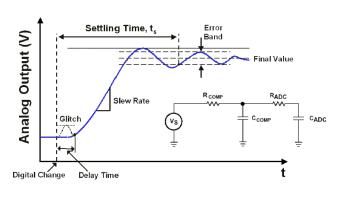

#### Précision du signal d'entrée :

Nous avons parlé du rapport signal sur bruit induit par le convertisseur, mais le SNR à l'entrée du convertisseur a une valeur minimum pour chaque résolution afin de ne pas introduire d'erreur d'un LSB. Une des composantes de ce bruit peut être le temps d'établissement du signal. Voici un tableau qui donne la valeur minimum du SNR et une illustration du temps d'établissement :

| Nb bits | SNR [dB] |  |

|---------|----------|--|

| 4       | 26       |  |

| 8       | 50       |  |

| 10      | 62       |  |

| 12      | 74       |  |

| 14      | 86       |  |

| 16      | 98       |  |

| 18      | 110      |  |

| 20      | 122      |  |

| 22      | 134      |  |

| 24      | 146      |  |

Figure 13: Bruit maximum et temps d'établissement en entrée de convertisseur

JPN 19/26 Avril 2023

#### Mesures et test de convertisseurs

Il va de soit que malgré toute l'attention que l'on peut porter à son développement, certains paramètres d'un circuit échappent à son concepteur et lors du câblage, de l'assemblage des composants, il peut arriver qu'une référence, une liaison, du bruit, ne soit pas au niveau où on l'attendait. Il ressort de ce fait, la nécessité de tester les caractéristiques de notre convertisseur monté sur son circuit avec tous les paramètres qui font la différence entre une data sheet parfaite et le « vrai » monde.

#### Test statique:

Pour vérifier les erreurs de linéarité, et d'offset, une mesure en introduisant une tension continue et en vérifiant le code généré peut s'avérer fort utile.

On peut afficher à l'aide de simples LED la valeur binaire de sortie du convertisseur et détecter les transitions lorsque deux LEDs sont partiellement allumées.

Figure 14: Mesure des transition entre deux codes

Une mesure « code centré » est difficile, c'est pourquoi il est préférable de mesurer les transitions entre les codes en étant conscient du décalage introduit.

Pour mesurer les valeurs de décalage et d'offset, quelques points au début et à la fin de la courbe sont suffisants. Il est clair que pour vérifier une erreur de code manquant ou de monotonicité, cette méthode qui passe par la mesure de chacun des seuils (255 pour un 8 bits) est longue et fastidieuse.

JPN 20/26 Avril 2023

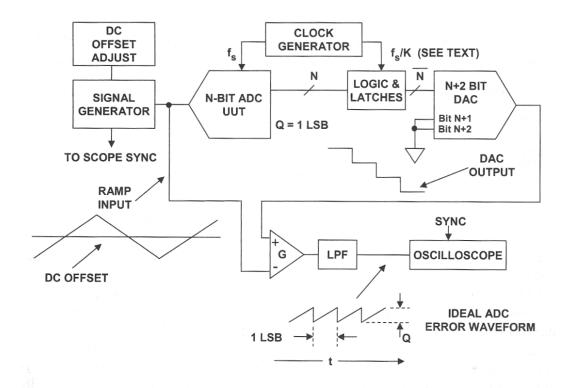

#### Méthode « dos à dos »:

Pour détecter des erreurs sur toute la plage de conversion, on peut utiliser cette méthode qui permet de vérifier la monotonicité, les codes manquants, et la non-linéarité différentielle d'un convertisseur.

Figure 15: Test statique dos à dos

Nous avons à gauche un générateur de signal qui fournit un signal triangle pas trop rapide, puis un convertisseur A/D à la sortie duquel on branche un convertisseur D/A et c'est la différence entre ces deux signaux (analogique d'entrée et analogique de sortie) que l'on va comparer et afficher à l'oscilloscope.

Le convertisseur D/A doit avoir une meilleure précision que le convertisseur A/D sous test, c'est pourquoi on a pris un D/A 14 bits pour contrôler un A/D 12 bits, les deux LSB du D/A sont à zéro.

#### Test par histogramme:

Un moyen simple de vérifier que le convertisseur a une réponse correcte est de lui imposer une rampe à l'entrée et de faire un histogramme des codes de sortie.

On détectera ainsi aisément les codes manquants et la non linéarité différentielle. Ce test ne donne par contre pas d'information concernant la monotonicité du convertisseur.

JPN 21/26 Avril 2023

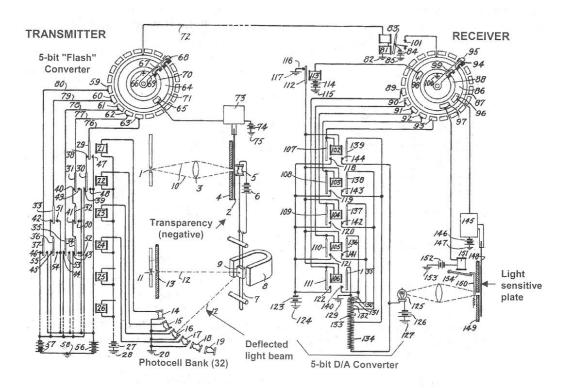

#### Convertisseur « Historique »:

The First Disclosure of PCM: Paul M. Rainey, "Facimile Telegraph System," U.S. Patent 1,608,527, Filed July 20, 1921,Issued November 30, 1926

#### Liens:

Analog device: Analog Dialogue 33-8 (1999)

http://www.analog.com/library/analogDialogue/archives/33-08/adc/

http://www.analog.com/technology/dataConverters/adc/index.html

http://dbserv.maxim-ic.com/tarticle/view\_article.cfm?article\_id=383

http://www.rmsinst.com/dt3.htm

http://pdfserv.maxim-ic.com/en/an/AN634.pdf

http://focus.ti.com/lit/an/slaa013/slaa013.pdf

Cours traitement signal et DSP

http://magphy.ujf-grenoble.fr/orbis/maitrise.html

Livre: Analog Device: Analog-Digital Conversion Ed: Walt Kester ISBN 0-916550-27-3

Notre site internet : www.electrons.ch

JPN 22/26 Avril 2023

#### **Exercices**

- 1. On a mesuré pour un convertisseur 16 bits un rapport signal sur bruit et distorsion de 75 dB. Déterminez le nombre effectif de bits de ce convertisseur. (*Réponse : 12*)

- 2. Enoncez le théorème de Shannon.

- 3. Illustrez à l'aide d'un exemple ce qu'est le repliement spectral.

- 4. Comment se protéger des erreurs dues au repliement spectral ?

- 5. Dessinez un schéma de principe d'un convertisseur Flash 3 bits.

- 6. Déterminez le rapport minimum entre la fréquence interne d'un convertisseur 10 bits à approximations successives et la fréquence de sortie des valeurs numériques (10 x).

- 7. Dessinez un exemple de convertisseur D/A 4 bits.

- 8. Illustrez une conversion SAR en montrant chaque étape graphiquement.

- 9. Donnez l'amplitude pic-pic du bruit de quantification pour un convertisseur 8 bits 5V f<sub>éch</sub>=20 kHz auquel on applique un signal triangulaire de 5Vpic-pic 10Hz.(*Réponse : 19mV*)

- 10. Calculez la valeur minimum du rapport signal sur bruit du signal d'entrée pour un A-D 8 bits ? (50dB)

- 11. Quelle est la différence entre SNR et SNAD?

- 12. Un convertisseur A/D 12 bits est utilisé pour échantillonner un signal 0-10V. Déterminez le rapport signal sur bruit du signal obtenu et la valeur crête à crête du bruit de quantification. (74dB;2.44mV)

- 13. A quoi sert le filtre anti-repliement ? Ou doit-on le placer dans la chaîne de conversion ?

- 14. Expliquez le fonctionnement d'un convertisseur FLASH en illustrant le fonctionnement à l'aide d'un dessin.

- 15. Donnez deux méthodes de vérification d'un convertisseur.

- 16. On place un convertisseur 10 bits derrière un ampli OP. Les résistances qui définissent son gain sont à 1%. Sans calibrage, quel est le nombre effectif de bits de l'ensemble ampliconvertisseur ? (1% correspond à 40dB, ce qui nous donne 6.35 bits de ENOB)

JPN 23/26 Avril 2023

17.

#### Exemples de data sheet

# 2.7 V to 5.5 V, 200 kSPS 8-Bit Sampling ADC

AD7819

FEATURES 8-Bit ADC with 4.5  $\mu s$  Conversion Time On-Chip Track and Hold Operating Supply Range: 2.7 V to 5.5 V Specifications at 2.7 V = 3.6 V and 5 V  $\pm$  10% 8-Bit Parallel Interface 8-Bit Read Power Performance Normal Operation 10.5 mW,  $V_{DD}=3$  V Automatic Power-Down 57.75  $\mu W$  @ 1 kSPS,  $V_{DD}=3$  V Analog Input Range: 0 V to  $V_{REF}$  Reference Input Range: 1.2 V to  $V_{DD}$

# VDD AGND VREF AD7819 CHARGE REDISTRIBUTION DAC CLOCK OSC THREESTATE DRIVERS CLOCK OSC DB0 CONTROL LOGIC

FUNCTIONAL BLOCK DIAGRAM

Figure 16: AD 7819

**Document Acrobat**

JPN 24/26 Avril 2023

#### TLC548C, TLC548I, TLC549C, TLC549I 8-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL

D OR P PACKAGE

(TOP VIEW)

REF+ [

REF-

GND [

3

ANALOG IN

SLAS067C - NOVEMBER 1983 - REVISED SEPTEMBER 199

7

6

$V_{CC}$

CS

I/O CLOCK

DATA OUT

- Microprocessor Peripheral or Standalone Operation

- 8-Bit Resolution A/D Converter

- Differential Reference Input Voltages

- Conversion Time . . . 17 μs Max

- Total Access and Conversion Cycles Per Second

- TLC548 . . . up to 45 500

- TLC549 . . . up to 40 000

- On-Chip Software-Controllable Sample-and-Hold Function

- Total Unadjusted Error . . . ±0.5 LSB Max

- 4-MHz Typical Internal System Clock

- Wide Supply Range . . . 3 V to 6 V

- Low Power Consumption . . . 15 mW Max

- Ideal for Cost-Effective, High-Performance Applications including Battery-Operated Portable Instrumentation

- Pinout and Control Signals Compatible With the TLC540 and TLC545 8-Bit A/D Converters and with the TLC1540 10-Bit A/D Converter

- CMOS Technology

**Figure 17: TLC 548**

Document Acrobat

JPN 25/26 Avril 2023

19-2955; Rev 0; 8/03

#### Multichannel, 14-Bit, 200ksps Analog-to-Digital Converters

#### General Description

The MAX1067/MAX1068 low-power, multichannel, 14-bit analog-to-digital converters (ADCs) feature a successive-approximation ADC, integrated +4.096V reference, a reference buffer, an internal oscillator, automatic power-down, and a high-speed SPI™/QSPI™/MICROWIRE™-compatible interface. The MAX1067/MAX1068 operate with a single +5V analog supply and feature a separate digital supply, allowing direct interfacing with +2.7V to +5.5V digital logic.

The MAX1067/MAX1068 consume only 2.9mA (AV<sub>DD</sub> = DV<sub>DD</sub> = +5V) at 200ksps when using an external reference. AutoShutdown™ reduces the supply current to 145μA at 10ksps and to less than 10μA at reduced sampling rates.

The MAX1067 includes a 4-channel input multiplexer, and the MAX1068 accepts up to eight analog inputs. In addition, digital signal processor (DSP)-initiated conversions are simplified with the DSP frame-sync input and output featured in the MAX1068. The MAX1068 includes a data-bit transfer input to select between 8-bit-wide or 16-bit-wide data-transfer modes. Both devices feature a scan mode that converts each channel sequentially or one channel continuously.

Excellent dynamic performance and low power, combined with ease of use and an integrated reference, make the MAX1067/MAX1068 ideal for control and data-acquisition operations or for other applications with demanding power consumption and space requirements. The MAX1067 is available in a 16-pin QSOP package, and the MAX1068 is available in a 24-pin QSOP package. Both devices are guaranteed over the commercial (0°C to +70°C) and extended (-40°C to +85°C) temperature ranges. Use the MAX1168 evalua-

#### Features

- 14-Bit Resolution, ±0.5 LSB INL and ±1 LSB DNL (max)

- ♦ +5V Single-Supply Operation

- Adjustable Logic Level (+2.7V to +5.25V)

- ♦ Input Voltage Range: 0 to VREF

- Internal (+4.096V) or External (+3.8V to AVDD)

Reference

- ♦ Internal Track/Hold, 4MHz Input Bandwidth

- Internal or External Clock

- SPI/QSPI/MICROWIRE-Compatible Serial Interface, MAX1068 Performs DSP-Initiated Conversions

- 8-Bit-Wide or 16-Bit-Wide Data-Transfer Mode (MAX1068 Only)

- 4-Channel (MAX1067) or 8-Channel (MAX1068) Input Mux

- Scan Mode Sequentially Converts Multiple Channels or One Channel Continuously

- ♦ Low Power

- 2.9mA at 200ksps

- 1.45mA at 100ksps

- 145µA at 10ksps

- 0.6µA in Full Power-Down Mode

- Small Package Size

- 16-Pin QSOP (MAX1067)

- 24-Pin QSOP (MAX1068)

**Figure 18: Max 1067**

**Document Acrobat**

JPN 26/26 Avril 2023